Learn about Micro SATA Cables and Computer Accessories

페이지 정보

작성자 Loretta 작성일24-07-31 13:49 조회16회 댓글0건관련링크

본문

The 68HC11 allows the details of the synchronous communications protocol to be customized for compatibility with a variety of peripherals. 3. Could you do customized functions according to requirements ? These detailed signal descriptions and cable diagrams are presented to provide complete information for those who have special communications requirements and for those who wish to make their own application-specific communications cables. The pinout of the Communications Connector (H14) is shown in Table 11 2, and the following diagrams show how these signals map to the two serial communications connectors. Regardless of the network, however, there are only four signals used: SCK provides a synchronized clock, MOSI and MISO signals are used for data transmission and reception, and /SS configures the 68HC11 as a master or slave device. There are a variety of ways the MOSI, MISO, SCK and /SS pins on your QVGA Controller can be connected. We have built sophisticated instruments using the QVGA Controller that operate very reliably using multiple interrupts in addition to the software UART. It’s important to note that all devices on the network need to use the same logic for interpreting voltage differences as bits (i.e., whether A being at a higher voltage than B represents a ‘1’ or a ‘0’).In a network with multiple devices, each device needs to have a unique address so that it knows when to listen and when to ignore the communications on the line.

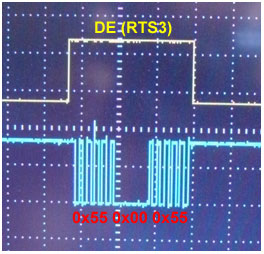

A mode fault occurs when the SPI senses that a multimaster conflict (MC68HC11F1 Technical Data Manual, p.10-5) exists on the network as explained above in connection with the /SS input. SPIE is a local interrupt mask that allows an interrupt to be recognized when an SPI data transfer has completed, or if a write collision or mode fault is detected. In each case, your QVGA Controller will be communicating at 19200 baud, and this baud rate will remain in effect until another BAUD1.AT.STARTUP command is executed, or until you invoke the Special Cleanup Mode as described earlier. Thus in Table 11 5 , RTS1 is connected to CTS1, and DSR1 is connected to DTR1 onboard the QVGA Controller using zero ohm shorting resistors. In this example, the QVGA Controller selects the serial A/D by outputting a LOW signal on /SS. We can gain insight into the operation of the RS232 protocol by examining the signal connections used for the primary serial port in Table 11 5. The transmit and receive data signals carry the messages being communicated between the QVGA Controller and the PC or terminal.

From the QVGA Controller’s point of view, these three signals (TxD, RxD, and ground) are the only connections required to perform serial communications. The DWOM bit (port D wired-or mode) should always be set to 0. Setting DWOM to 1 takes away the processor’s ability to pull the Port D signals high unless there is a pull-up resistor on each bit of the port. For example, at 4800 baud (bits per second), each bit lasts about 200 microseconds (µs), and if communications are full duplex (e.g., if the QVGA Controller echoes each incoming character), then there is a serial interrupt every 100 µs or so. If bit 5 of DDRD is 1, then /SS is a general purpose output that operates independently of the SPI. If the /SS input to a slave is inactive (high), the slave ignores the SCK input, does not transmit or receive data, and keeps its MISO output in a high-impedance state so that it does not interfere with the SPI bus. Hardware is interfaced to the SPI via four PORTD pins named /SS, SCK, MOSI, and MISO brought out to pins 11 through 14 on the Digital I/O connector (see Appendix A).

The QED-Forth kernel includes pre-coded drivers that configure the SPI for maximum speed data transfer using a format that is compatible with the on-board D/A and 12 bit A/D. Setting the MSTR bit initializes the QScreen as a master, and clearing the MSTR bit initializes it as a slave. In this situation, if the /SS input is pulled low while the 68HC11 is the master, the processor detects a "mode fault" (by setting a bit in the SPI status register) meaning that there is more than one master device on the SPI bus. A mode fault occurs when the SPI senses that a multimaster conflict (MC68HC11F1 Technical Data Manual, p.8-7) exists on the network as explained above in connection with the /SS input. The QVGA Controller’s on-board 12 bit A/D and 8 bit D/A converters communicate with the processor via the SPI. If bit 5 of DDRD is 0, then /SS is an input.

When you loved this post and you would want to receive more information regarding what is rs485 cable please visit our own website.

댓글목록

등록된 댓글이 없습니다.